Adaptive & Secure Computing Systems (ASCS) Laboratory

Technical Areas: Hardware security, hardware root-of-trust, post-quantum cryptography, homomorphic encryption, multi party computation, secure architecture, reconfigurable computing, Adaptive Computing.

Current Projects

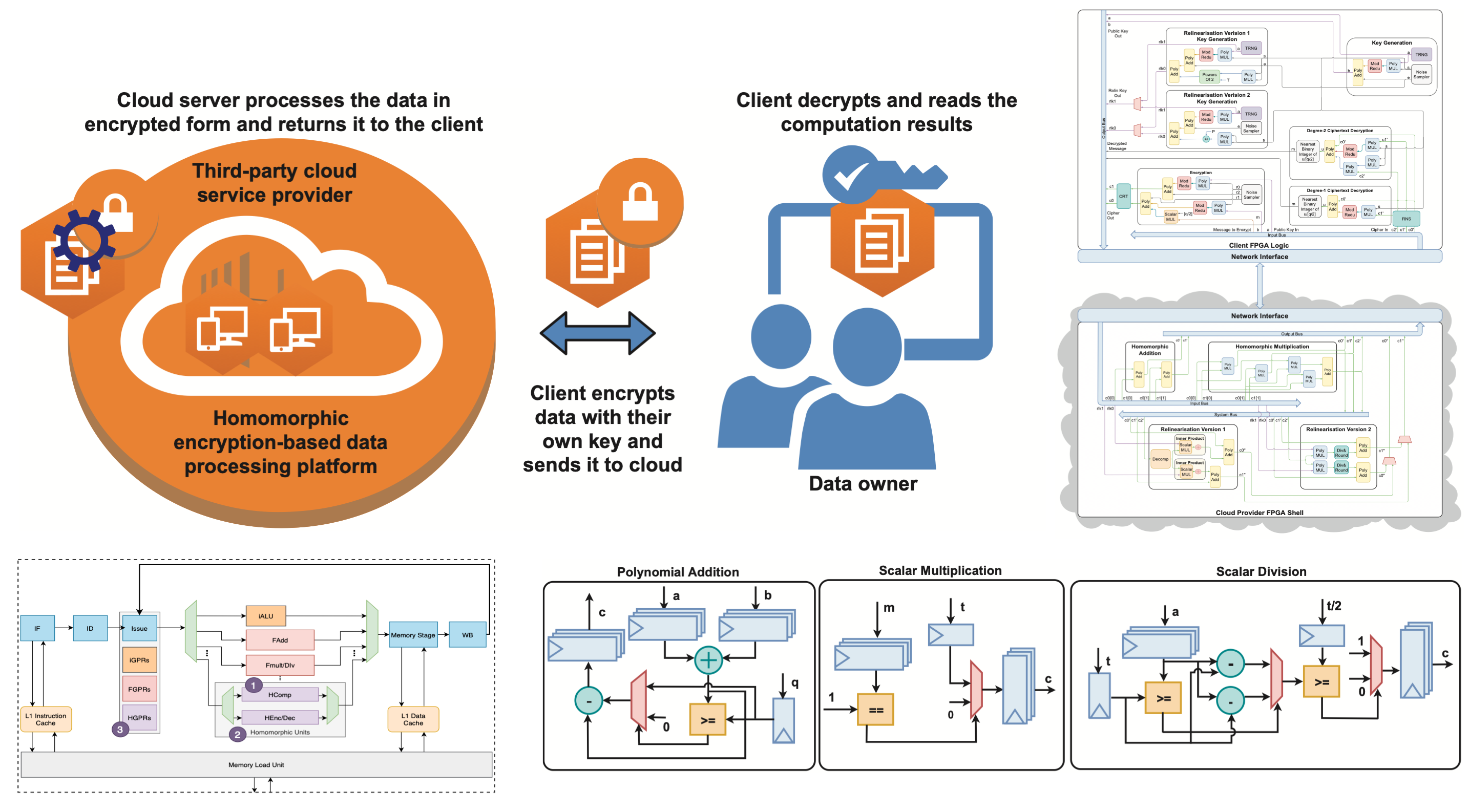

Homomorphic-Encryption Enabled RISC-V (HERISCV) Architecture

Large Arithmetic Word Size (LAWS): Word size directly relates to the signal-to-noise ratio (SNR) of how a ciphertext is stored and manipulated in computation. There currently is no hardware architecture that natively supports the register sizes and/or the execution units performing the fundamental mathematical and logical operations for lattice FHE schemes.

ISA Based Reconfigurable Architecture: Given the evolving state of improvements and new schemes in the field of FHE, the HERISCV architecture aims to provide an array of operations and functionality instead of optimizing the hardware for one particular algorithm. The architecture provides significant performance gains for lattice-based FHE applications as well as the flexibility to experiment with new designs by having instruction support for the core operations, e.g., lattices, polynomials, arithmetic, logic and finite fields.

Publications

- M. A. Kinsy: “Post-quantum Cryptographic Hardware Primitives”, In: Jajodia S., Samarati P., Yung M. (eds) Encyclopedia of Cryptography, Security and Privacy. Springer, Berlin, Heidelberg, 2021.