Computer Architecture and Embedded Systems (CAES) Laboratory

Technical Areas: Computer Architecture, Embedded systems, RISC-V, high performance computing, supercomputing, Edge computing, hardware root-of-trust, system-on-chip design.

Current Projects

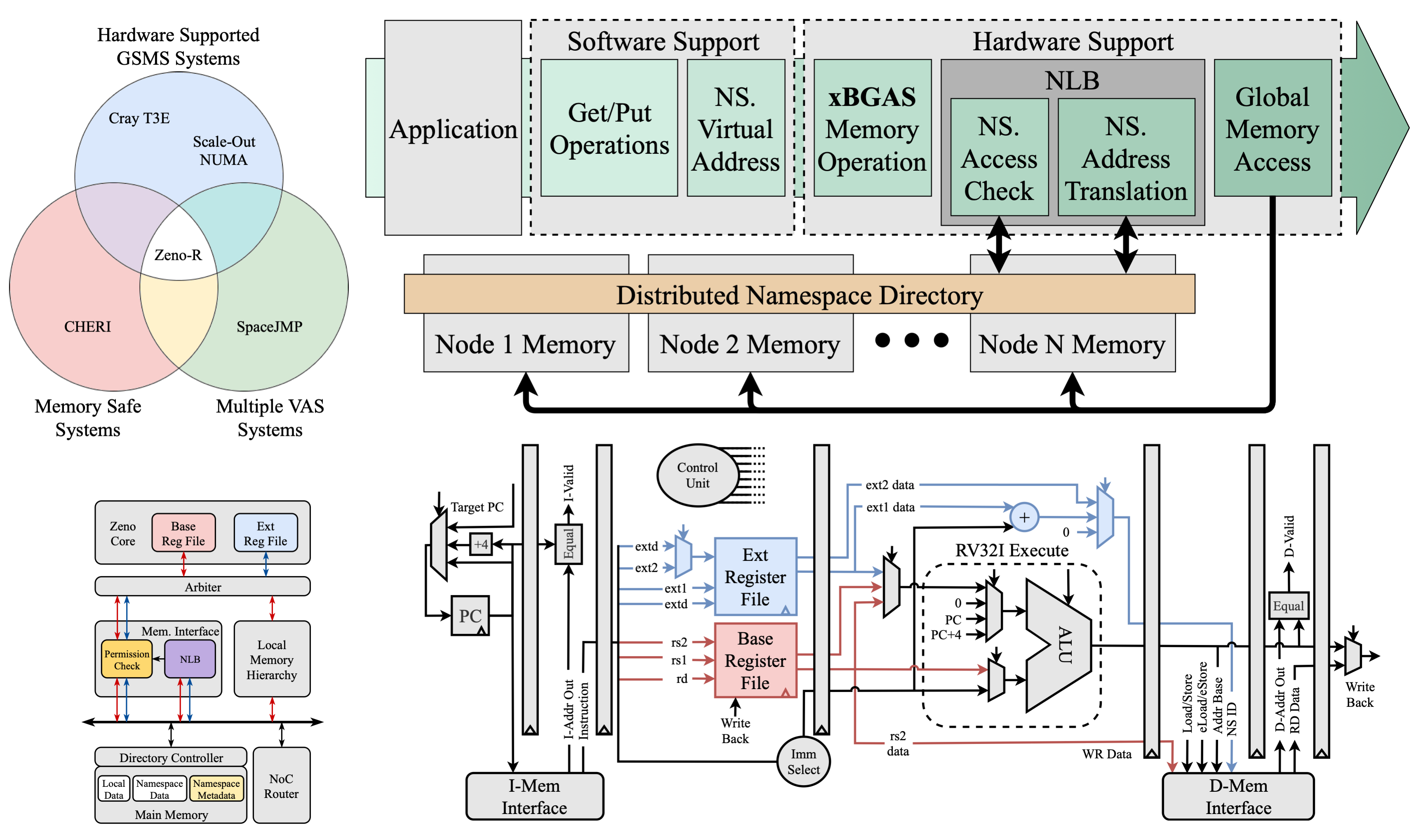

Hardware-assisted secure HPC/data-center scale shared memory: Zeno is a new security-aware scalable architecture for shared, distributed memory, high performance computing (HPC) systems. Its micro-architectural support for shared memory enables security-aware data sharing between different processors in a single HPC system without hindering scalability.

Zeno Architecture: A Secure High-Performance Computing RISC-V Processor Design

The traditional evolution of the HPC field has created an ecosystem where oftentimes a small number of systems would be commissioned by a government agency through a computer system vendor using (i) proprietary intellectual property (IP) blocks and (ii) obscure or rigid system architecture.

One can argue that the lack of open-architecture concepts in HPC and server-class systems has severely hindered innovation in the field. System-level security-related research efforts are generally altogether abandoned due to the lack of visibility or access to micro-architecture details to test, analyze or validate vulnerabilities, threats or risks.

Under this research effort, the team has introduced a new open-source server architecture, called Zeno, where high-performance and security are both first class system characteristics.

The Zeno architecture specifications, synthesized design, system support software, and programming tools will be open-sourced.

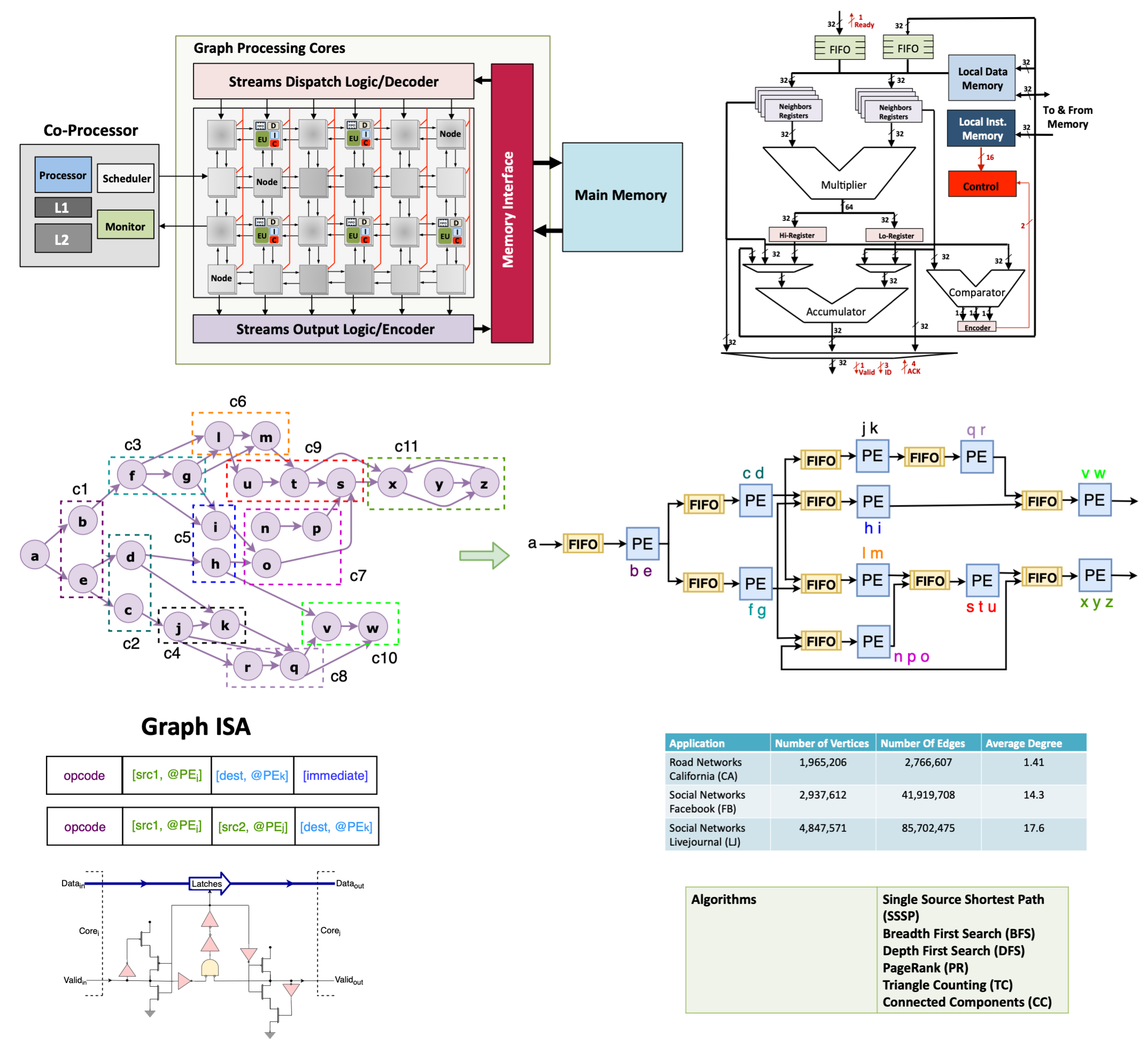

High-Performance Asynchronous Graph Processor

Graph algorithms and techniques are increasingly used in scientific and commercial applications to express relations and explore large data sets.

In this work, we propose and design a new architecture, called Plexus, for the fast processing of large graph applications. To leverage the lack of the spatial and temporal localities in these applications and to support scalable computational models, we design the architecture around two key concepts.

The architecture is a multicore processor of independently clocked processing elements. These elements communicate in a self-timed manner and use handshaking to perform synchronization, communication, and sequencing of operations. By being asynchronous, the operating speed at each processing element is determined by actual local latencies rather than global worst-case latencies. We experience with a specialized ISA to support these operations.

We are currently refining the design using a parameterized design approach

with RISC-V ISA. Parameterization will help us in shrinking or expanding the datapath size as required. Moreover, adapting to RISC-V core will also help us in leveraging the support of the existing software ecosystem.

Publications

- J. Abraham, A. Ehret, and M. A. Kinsy: “A Compiler for Transparent Namespace-Based Access Control for the Zeno Architecture”, In the International Symposium on Secure and Private Execution Environment Design (SEED), 2022.

- X. Wang, B. Williams, J. D. Leidel, A. Ehret, M. Mark, M. A. Kinsy and Y. Chen: “xBGAS: A Global Address Space Extension on RISC-V for High Performance Computing”, In the 35th IEEE International Parallel & Distributed Processing Symposium (IPDPS), 2021. Best Paper Award