Laboratory for Unconventional Computing Substrates (LUCS)

Current Projects

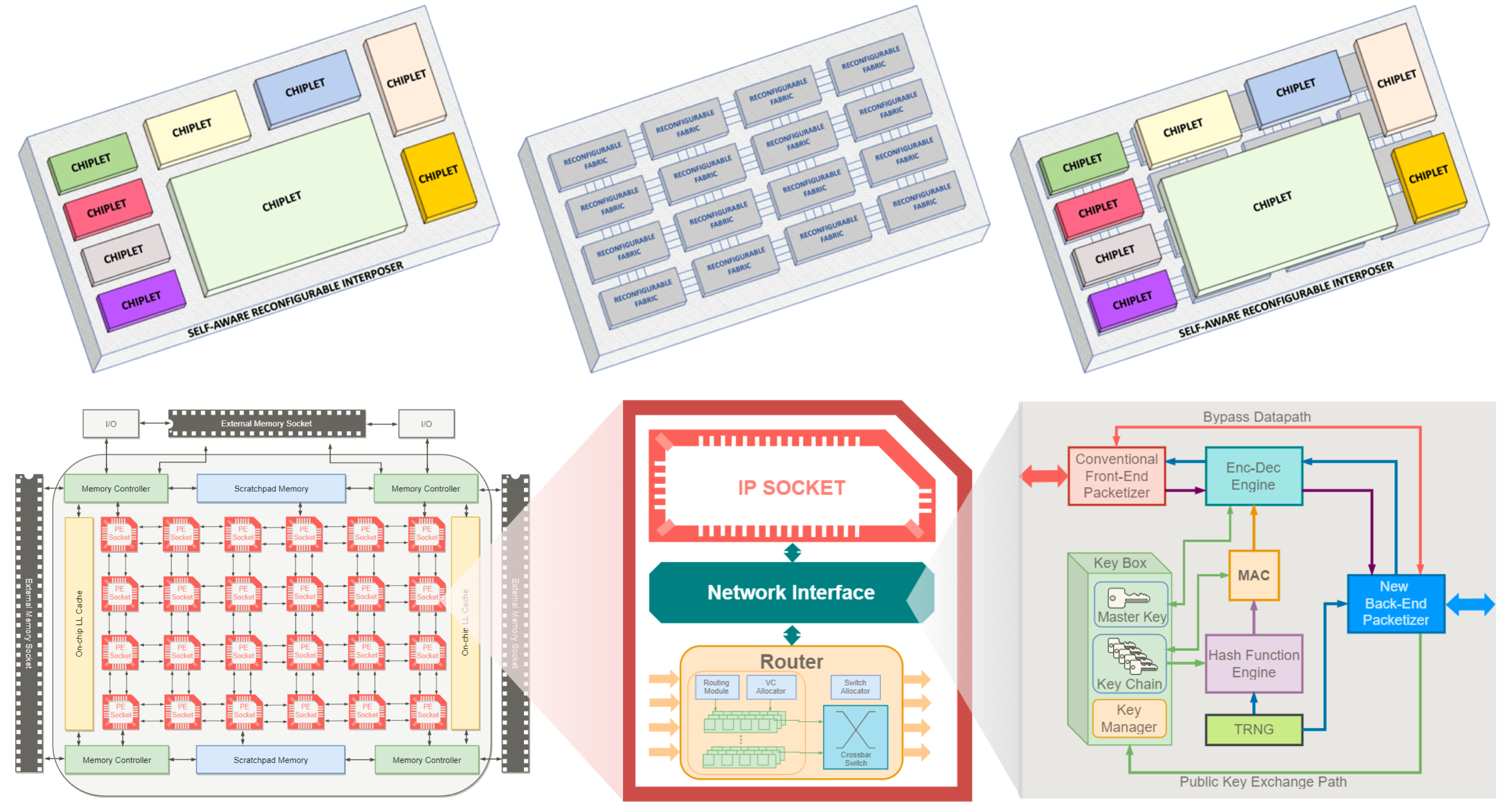

Using Security-Aware Reconfigurable Interposers: A new active interposer 2.5-D design methodology using reconfigurable logic targeting security applications.

Zero-Trust SoC Design: Building Secure System-on-Chip Designs from Untrusted Components

On SoC platforms consisting of multiple or a multitude of processing elements, the runtime interactions between processing elements can be very complex and difficult to fully analyze at design time.

The key innovation of the approach is that security is provided through (i) hardware virtualization that is completely independent of the processing elements themselves, and (ii) runtime establishment of trust among the elements.

The approach aims to reduce the system’s attack surface by creating a virtualization layer that isolates compute threads based on system and user-defined trust levels and security policies.

We imbue the active interposer with reconfigurable fabric that can be programmed at integration and end-use stages to provide hardware root-of-trust security guarantees.

Publications

- P. Yellu, L. Buell, M. Mark, M. Kinsy, D. Xu, Q. Yu: “Security Threat Analyses and Attack Models for Approximate Computing Systems: From Hardware and Micro-Architecture Perspectives”, Transactions on Design Automation of Electronic Systems (TODAES), In Press 2021.